# ATME COLLEGE OF ENGINEERING

13th Km Stone, Bannur Road, Mysore - 570028

# DEPARTMENT OF ELECTRICAL & ELECTRONICS ENGINEERING

(ACADEMIC YEAR 2024-25)

# LABORATORY MANUAL

# **BEE303-Analog Electronic Circuits**

Prepared By Verified By Approved by

Dr.Sathish KR Assistant Professor Dept. of EEE., ATMECE Mr. Shreeshayana R Assistant Professor Dept. of EEE., ATMECE

HOD

Dept. of EEE., ATMECE

#### **Vision of the Institute**

Development of academically excellent, culturally vibrant, socially responsible and globally competent human resources.

#### **Mission of the Institute**

- To keep pace with advancements in knowledge and make the students competitive and capable at the global level.

- To create an environment for the students to acquire the right physical, intellectual, emotional and moral foundations and shine as torch-bearers of tomorrow's society.

- To strive to attain ever-higher benchmarks of educational excellence

### **Vision of the Department**

To create Electrical and Electronics Engineers who excel to be technically competent and fulfill the cultural and social aspirations of the society.

# **Mission of the Department**

- To provide knowledge to students that builds a strong foundation in the basic principles of electrical engineering, problem solving abilities, analytical skills, soft skills and communication skills for their overall development.

- To offer outcome based technical education.

- To encourage faculty in training & development and to offer consultancy through research & industry interaction.

|             | BEE303-Analog Electronic Circuits                                  |                                                                  |                       |                      |  |

|-------------|--------------------------------------------------------------------|------------------------------------------------------------------|-----------------------|----------------------|--|

| IPCC Cou    | IPCC Course Code                                                   |                                                                  | CIE Marks             | 25                   |  |

| Number o    | Number of Practical                                                |                                                                  | Total Hours/          | 10 Lab               |  |

| Hours/We    | Hours/Week                                                         |                                                                  | Sessions              | slots                |  |

|             |                                                                    |                                                                  |                       |                      |  |

|             |                                                                    | Credits                                                          | - 04                  |                      |  |

| Sl. No      |                                                                    |                                                                  | periments             |                      |  |

| 01          | Experiments on                                                     | series, shunt ar                                                 | nd double ended clipp | pers and clampers.   |  |

|             | Design and Te                                                      | esting of Full                                                   | wave - centre ta      | pped transformer     |  |

| 02          | type and Brid                                                      | dge type re                                                      | ctifier circuits w    | ith and without      |  |

| 02          | Capacitor filter                                                   | r. Determinat                                                    | ion of ripple factor  | r, regulation and    |  |

|             | efficiency                                                         |                                                                  |                       |                      |  |

| 02          | Static Transistor                                                  | r characteristi                                                  | cs for CE, CB and     | d CC modes and       |  |

| 03          | determination of h parameters                                      |                                                                  |                       |                      |  |

|             | Frequency response of single stage BJT and FET RC coupled          |                                                                  |                       |                      |  |

| 04          | amplifier and determination of half power points, bandwidth, input |                                                                  |                       |                      |  |

|             | and output imped                                                   | dances.                                                          |                       |                      |  |

| 0.7         | Design and tes                                                     | ting of BJT-                                                     | RC phase shift os     | cillator for given   |  |

| 05          | frequency of osc                                                   | illation.                                                        |                       | _                    |  |

| 0.1         | Design and tes                                                     | Design and testing of Hartley and Colpitt's oscillator for given |                       |                      |  |

| 06          | frequency of osc                                                   |                                                                  |                       | -                    |  |

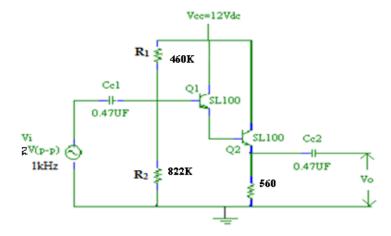

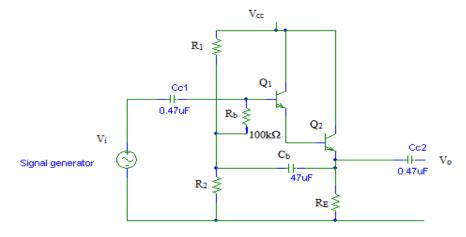

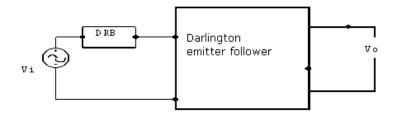

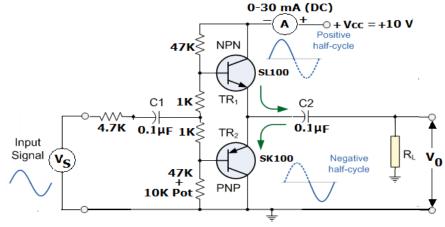

| 0.7         | Determination of                                                   | f gain, input ar                                                 | nd output impedance   | of BJT Darlington    |  |

| 07          | emitter follower                                                   | with and withou                                                  | out bootstrapping.    |                      |  |

| 00          | Design and testi                                                   | ing of Class A                                                   | and Class B power     | er amplifier and to  |  |

| 08          | determine conve                                                    | rsion efficienc                                                  | y                     | _                    |  |

| 09          | Design, simulati                                                   | on (MATLAB                                                       | ) and testing of Wie  | en bridge oscillator |  |

| 09          | for given frequer                                                  | ncy of oscillation                                               | on.                   |                      |  |

|             |                                                                    |                                                                  | wave – centre tappe   |                      |  |

| 10          |                                                                    |                                                                  | uits with and witho   |                      |  |

| 10          |                                                                    | <ol><li>Determinat</li></ol>                                     | ion of ripple factor  | or, regulation and   |  |

| efficiency. |                                                                    |                                                                  |                       |                      |  |

#### **Conduct of Practical Examination:**

- 1. All laboratory experiments are to be included for practical examination.

- 2. Breakup of marks and the instructions printed on the cover page of answer script to be strictly adhered by the examiners.

- 3. Students can pick one experiment from the questions lot prepared by the examiners.

- 4. Change of experiment is allowed only once and 15% Marks allotted to the procedure part to be made zero.

| Sl. No | Cycle –I Experiments                                                                                                                                                                                              |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01     | Experiments on series, shunt and double ended clippers and clampers.                                                                                                                                              |

| 02     | Design and Testing of Full wave – centre tapped transformer type and Bridge type rectifier circuits with and without Capacitor filter. Determination of ripple factor, regulation and efficiency                  |

| 03     | Static Transistor characteristics for CE, CB and CC modes and determination of h parameters                                                                                                                       |

| 04     | Frequency response of single stage BJT and FET RC coupled amplifier and determination of half power points, bandwidth, input and output impedances.                                                               |

| 05     | Design and testing of BJT-RC phase shift oscillator for given frequency of oscillation.                                                                                                                           |

|        | Cycle –II Experiments                                                                                                                                                                                             |

| 06     | Design and testing of Hartley and Colpitt's oscillator for given frequency of oscillation.                                                                                                                        |

| 07     | Determination of gain, input and output impedance of BJT Darlington emitter follower with and without bootstrapping.                                                                                              |

| 08     | Design and testing of Class A and Class B power amplifier and to determine conversion efficiency.                                                                                                                 |

| 09     | Design, simulation (MATLAB) and testing of Wien bridge oscillator for given frequency of oscillation.                                                                                                             |

| 10     | Design and simulation of Full wave – centre tapped transformer type and Bridge type rectifier circuits with and without Capacitor filter using MATLAB. Determination of ripple factor, regulation and efficiency. |

### Program Outcomes (PO's)

**PO1:Engineering Knowledge**: Apply the knowledge of mathematics, science, engineering fundamentals and an engineering specialization to the solution of complex engineering problems.

**PO2: Problem Analysis:** Identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences.

**PO3: Design / Development of Solutions:** Design solutions for complex engineering problems and design system components or processes that meet the specified needs with appropriate consideration for the public health and safety, and the cultural, societal, and environmental considerations.

**PO4:** Conduct Investigations of Complex Problems: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

**PO5:** Modern Tool Usage: Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools including prediction and modeling to complex engineering activities with an understanding of the limitations.

**PO6:** The Engineer and Society: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

**PO7:** Environment and Sustainability: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

**PO8: Ethics:** Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

**PO9: Individual and Team Work:** Function effectively as an individual and as a member or leader in diverse teams, and in multidisciplinary settings.

**PO10:** Communication: Communicate effectively on complex engineering activities with the engineering community and with society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions.

**PO11: Project Management and Finance:** Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

**PO12: Life-Long Learning:** Recognize the need for and have the preparation and ability to engage in independent and lifelong learning in the broadest context of technological change.

### **Program Specific Outcomes (PSO's)**

**PSO1:** Apply the concepts of Electrical & Electronics Engineering to evaluate the performance of power systems and also to control industrial drives using power electronics.

**PSO2:** Demonstrate the concepts of process control for Industrial Automation, design models for environmental and social concerns and also exhibit continuous self-learning.

# **Program Educational Objectives (PEO's)**

PEO1: To produce competent and ethical Electrical and Electronics Engineers who will exhibit the necessary technical and managerial skills to perform their duties in society.

PEO2: To make graduates continuously acquire and enhance their technical and socio-economic skills.

PEO3: To aspire graduates on R&D activities leading to offering solutions and excel in various career paths.

PEO4: To produce quality engineers who have the capability to work in teams and contribute to real time projects.

### **Identification of Circuit Components**

#### **Breadboards:**

in order to temporarily construct a circuit without damaging the components used to build it, we must have some sort of a platform that will both hold the components in place and provide the needed electrical connections. In the early days of electronics, most experimenters were amateur radio operators. They constructed their radio circuits on wooden breadboards. Although more sophisticated techniques and devices have been developed to make the assembly and testing of electronic circuits easier, the concept of the breadboard still remains in assembling components on a temporary platform.

a. Typical breadboard

**b.** Connection details

A real breadboard is shown in Fig. 1(a) and the connection details on its rear side are shown in Fig. 1(b). The five holes in each individual column on either side of the central groove are electrically connected to each other, but remain insulated from all other sets of holes. In addition to the main columns of holes, however,

you'll note four sets or groups of holes along the top and bottom. Each of these consists of five separate sets of five holes each, for a total of 25 holes. These groups of 25 holes are all connected together on either side of the dotted line indicated on Fig.1(a) and needs an external connection if one wishes the entire row to be connected. This makes them ideal for distributing power to multiple ICs or other circuits.

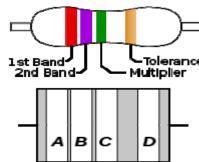

#### **Resistors:**

| Band<br>Color | Digit | Multiplier  | Tolerance |        |

|---------------|-------|-------------|-----------|--------|

| Black         | 0     | 1           | 7222      | $\Box$ |

| Brown         | 1     | 10          | ±1%       |        |

| Red           | 2     | 100         | ±2%       |        |

| Orange        | 3     | 1,000       | ±3%       | 1st Ba |

| Yellow        | 4     | 10,000      | ±4%       | 2nd B  |

| Green         | 5     | 100,000     | ***       | _      |

| Blue          | 6     | 1,000,000   | 1444      |        |

| Violet        | 7     | 10,000,000  | (many)    |        |

| Gray          | 8     | 100,000,000 |           |        |

| White         | 9     |             |           |        |

| Gold          | W.775 | 0.1         | ±5%       |        |

| Silver        | ***   | 0.01        | ±10%      |        |

| None          |       | 9 5         | ±20%      | _      |

- band A is first significant figure of component value

- band B is the second significant figure

- band C is the decimal multiplier

- band D if present, indicates tolerance of value in percent (no color means 20%)

For example, a resistor with bands of yellow, violet, red, and gold will have first digit 4 (yellow in table below), second digit 7 (violet), followed by 2 (red) zeros: 4,700 ohms. Gold signifies that the tolerance is  $\pm 5\%$ , so the real resistance could lie anywhere between 4,465 and 4,935 ohms.

Tight tolerance resistors may have three bands for significant figures rather than two, and/or an additional band indicating temperature coefficient, in units of ppm/K. For large power resistors and potentiometers, the value is usually written out implicitly as " $10 \text{ k}\Omega$ ", for instance.

### **Capacitors:**

You will mostly use electrolytic and ceramic capacitors for your experiments.

### **Electrolytic capacitors**

An electrolytic capacitor is a type of capacitor that uses an electrolyte, an ionic conducting liquid, as one of its plates, to achieve a larger capacitance per unit volume than other types. They are used in relatively high-current and low-frequency electrical circuits. However, the voltageapplied to these capacitors must be polarized; one specified terminal must always have positive potential with respect to the other. These are of two types, axial and radial capacitors as shown in adjacent figure. The arrowed stripe indicates the polarity, with the arrows pointing towards the negative pin.

**Warning:** connecting electrolytic capacitors in reverse polarity can easily damage or destroy the capacitor. Most large electrolytic capacitors have the voltage, capacitance, temperature ratings, and company name written on them without having any special color coding schemes.

Axial electrolytic capacitors have connections on both ends. These are most frequently used in devices where there is no space for vertically mounted capacitors.

Radial electrolytic capacitors are like axial electrolytic ones, except both pins come out the same end. Usually that end (the "bottom end") is mounted flat against the PCB and the capacitor rises perpendicular to the PCB it is mounted on. This type of capacitor probably accounts for at least 70% of capacitors in consumer electronics.

**Ceramic capacitors** are generally non-polarized and almost as common as radial electrolytic capacitors. Generally, they use an alphanumeric marking system. The number part is the same as for SMT resistors, except that the value represented is in pF. They may also be written out directly, for instance, 2n2 = 2.2 nF.

#### **Diodes:**

A standard specification sheet usually has a brief description of the diode. Indescription is the type of diode, the major area of application, and any specific particular interest is the specific application for which the diode is suited. Theyalso provides a drawing of the diode which gives dimension, weight, and, if approximate identification marks. In addition to the above data, the following information is provided: a static operating table (giving spot values of parameters under fixsometimes a characteristic curve (showing how parameters vary over the range), and diode ratings (which are the limiting values of operating conditionscould cause diode damage). Manufacturers specify these various diode operations

and characteristics with "letter symbols" in accordance with fixed definitions.

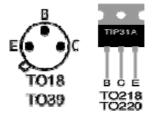

#### **Transistors:**

Transistor are identified by a Joint-Navy (JAN) designation printed directly on thecase of the transistor. If in doubt about a transistor's markings, always replace a transistor with one having identical markings, or consult an equipment or transistor manual to ensure that an identical replacement or substitute is used. Example:

2 N 130 A

NUMBER OF JUNCTIONS SEMICONDUCTOR IDENTIFICATION FIRST MODIFICATION

Identifying the transistor

# Testing with a multimeter

Transistor Resistance Values for the PNP and NPN transistor types

| Between Transistor Terminals |           | PNP               | NPN               |

|------------------------------|-----------|-------------------|-------------------|

| Collector                    | Emitter   | R <sub>HIGH</sub> | R <sub>HIGH</sub> |

| Collector                    | Base      | R <sub>LOW</sub>  | R <sub>HIGH</sub> |

| Emitter                      | Collector | R <sub>HIGH</sub> | R <sub>HIGH</sub> |

| Emitter                      | Base      | R <sub>LOW</sub>  | R <sub>HIGH</sub> |

| Base                         | Collector | R <sub>HIGH</sub> | $R_{LOW}$         |

| Base                         | Emitter   | R <sub>HIGH</sub> | R <sub>LOW</sub>  |

### **Experiment No: 01**

#### Date:

### Experiments on series, shunt and double ended clippers and clampers.

**Objective:** To design and test diode clipping circuits for peak clipping and peak detection and Design and test positive and negative clamping circuit for a given reference voltage

### **Apparatus Required:**

| SL. No | Particular               | Range    | Quantity    |

|--------|--------------------------|----------|-------------|

| 1      | Bread board              |          | 1           |

| 2      | CRO                      |          | 1           |

| 3      | Power supply             | DC 0-30V | 2           |

| 5      | Diodes                   | 1N4007   | 1           |

| 6      | Resistors                | 1ΚΩ      | 1           |

| 7      | Function generator       |          |             |

| 8      | Connecting wire and prob |          | As required |

### Theory:

A transistor is a three terminal device. The terminals are emitter, base, collector. In common emitter configuration, input voltage is applied between base and emitter terminals and output is taken across the collector and emitter terminals. Therefore the emitter terminal is common to both input and output. The input characteristics resemble that of a forward biased diode curve. This is expected since the Base-Emitter junction of the transistor is forward biased. As compared to CB arrangement  $I_B$  increases less rapidly with  $V_{BE}$ . Therefore input resistance of CE circuit is higher than that of CB circuit. The output characteristics are drawn between Ic and  $V_{CE}$  at constant  $I_B$ , the collector current varies with  $V_{CE}$  unto few volts only. After this the collector current becomes almost constant, and independent of  $V_{CE}$ . The value of  $V_{CE}$  up to which the collector current changes with  $V_{CE}$  is known as Knee voltage. The transistor always operated in the region above Knee voltage,  $I_C$  is always constant and is approximately equal to  $I_B$ .

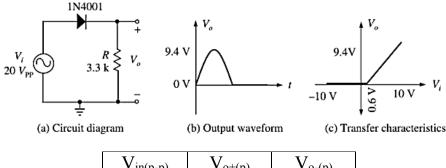

# **Series Negative Clipper Circuit (Unbiased)**

| $V_{in(p-p)}$ | $V_{o+(p)}$ | $V_{o-(p)}$ |

|---------------|-------------|-------------|

| 8V            |             |             |

| 12V           |             |             |

| 20V           |             |             |

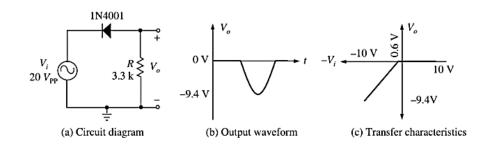

# **Series Positive Clipper Circuit (Unbiased)**

| $V_{in(p-p)}$ | $V_{o+(p)}$ | $V_{o-(p)}$ |

|---------------|-------------|-------------|

| 8V            |             |             |

| 12V           |             |             |

| 20V           |             |             |

Page 6

AY 2023-24

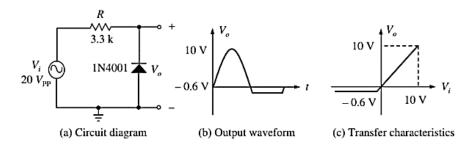

# **Shunt Negative Clipper Circuit (Unbiased)**

| $V_{in(p-p)}$ | $V_{o+(p)}$ | $V_{o-(p)}$ |

|---------------|-------------|-------------|

| 8V            |             |             |

| 12V           |             |             |

| 20V           |             |             |

# **Shunt Positive Clipper Circuit (Unbiased)**

| $V_{in(p-p)}$ | $V_{o+(p)}$ | $V_{o-(p)}$ |

|---------------|-------------|-------------|

| 8V            |             |             |

| 12V           |             |             |

| 20V           |             |             |

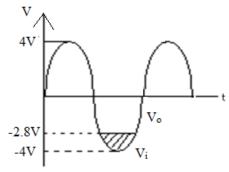

# Diode shunt clipping (Positive peak clipping with positive bias voltage)

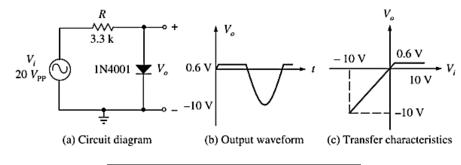

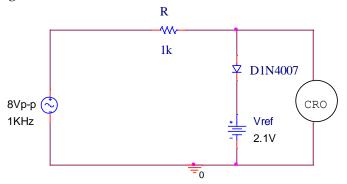

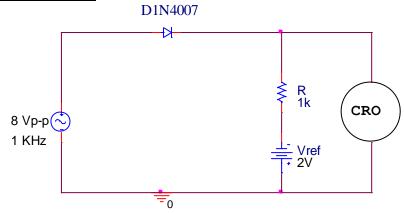

Circuit diagram:

Fig.1.1: Circuit diagram of Diode shunt clipping (Positive peak clipping with positive bias voltage)

### Design:

Let the output voltage to be clipped at 2.8V i,e Vo(max)=2.8V

But Vo(max)=Vd+Vref

Where Vd= diode forward voltage drop=0.7V

$$\therefore V_{\text{ref}} = V_{\text{o(max)}} - V_{\text{d}} = 2.8 - 0.7 = 2.1 \text{V}$$

Choose the value of R such that the current in the circuit must lie between 1mA to 10mA.

Let current be 1mA

Then

$$R = \frac{V_{i(max)} - V_{o(max)}}{I} = \frac{4 - 2.8}{1.5m} = 800\Omega$$

Choose  $R=1K\Omega$

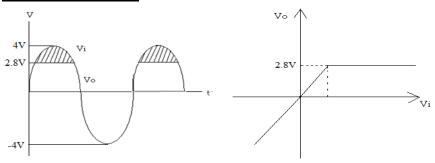

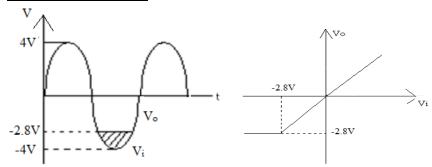

# **Expected waveform:**

Fig. 1.2: output waveform and transfer characteristics

# **Tabular column:**

| V <sub>i(p-p)</sub> | $V_{ref}$ | $V_{o+(p)}$ | V <sub>o-(p)</sub> |

|---------------------|-----------|-------------|--------------------|

| <b>6V</b>           | 2.1       |             |                    |

| <b>8V</b>           | 2.1       |             |                    |

| 10V                 | 2.1       |             |                    |

| 12V                 | 2.1       |             |                    |

<u>Diode shunt clipping (Negative peak clipping</u> with Negative bias voltage)

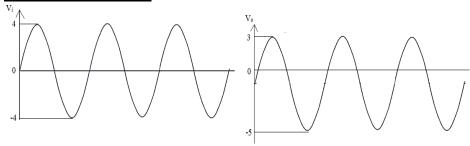

# **Circuit diagram:**

Fig.1.5: Diode shunt clipping (Negative peak clipping)

### **Design:**

Let the output voltage to be clipped at 2.8V i,e  $V_{o(max)}$ = - 2.8V

But

$$V_{o(min)} = -(V_d + V_{ref})$$

Where  $V_d$ = diode forward voltage drop=0.7V

$$\therefore -V_{\text{ref}} = V_{\text{o(min)}} - V_{\text{d}} = -2.8 + 0.7 = -2.1V$$

Choose the value of R such that the current in the circuit must lie between 1mA to 10mA.

Let current be 1mA

Then

$$R = \frac{V_{i(max)} - V_{o(max)}}{I} = \frac{4 - 2.8}{1.5m} = 8000$$

Choose  $R=1K\Omega$

### **Expected waveform:**

Fig. 1.6: Output waveform and transfer characteristics

# **Tabular column:**

| V <sub>i(p-p)</sub> | Vref | V <sub>o+(p)</sub> | V <sub>o-(p)</sub> |

|---------------------|------|--------------------|--------------------|

| 6V                  | 2.1  |                    |                    |

| <b>8V</b>           | 2.1  |                    |                    |

| 10V                 | 2.1  |                    |                    |

| 12V                 | 2.1  |                    |                    |

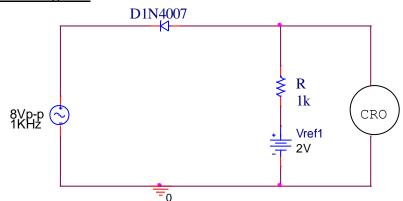

# Diode series clipping (Positive peak clipping with Positive bias voltage)

### Circuit diagram:

Fig. 1.7: Diode series clipping circuit (Positive peak clipping with **Positive bias voltage)**

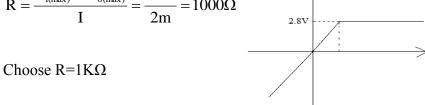

# **Design:**

Let the output voltage to be clipped at 2V i,e  $V_{o(max)}=V_{ref}=2V$

Choose the value of R such that the current in the circuit must lie between 1mA to 10mA.

### Let current be 2mA

Then

$$R = \frac{V_{i(max)} - V_{o(max)}}{I} = \frac{4 - 2}{2m} = 1000\Omega$$

vo /

# **Expected waveform:**

Fig. 1.8: Output waveform and transfer characteristics

# **Tabular column:**

| V <sub>i(p-p)</sub> | $V_{ref}$ | $V_{o+(p)}$ | V <sub>0-(p)</sub> |

|---------------------|-----------|-------------|--------------------|

| 6V                  | 2.0       |             |                    |

| <b>8V</b>           | 2.0       |             |                    |

| 10V                 | 2.0       |             |                    |

| 12V                 | 2.0       |             |                    |

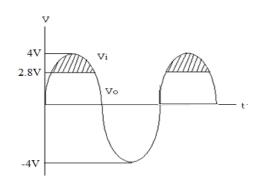

# Diode series clipping (Negative peak clipping with Negative bias voltage)

# Circuit diagram:

Fig. 1.9: Diode series clipping circuit (Negative peak clipping with Negative bias voltage)

# **Design:**

Let the output voltage to be clipped at 2V i,e  $V_{o(max)} = V_{ref} = 2V$

Choose the value of R such that the current in the circuit must lie between 1mA to 10mA.

Let current be 2mA

Then

$$R = \frac{V_{i(max)} - V_{o(max)}}{I} = \frac{4-2}{2m} = 1000\Omega$$

Choose  $R=1K\Omega$

# **Expected waveform:**

Fig. 1.10: Output waveform and transfer characteristics <u>Tabular column:</u>

| V <sub>i(p-p)</sub> | Vref | V <sub>0+(p)</sub> | V <sub>0</sub> -(p) |

|---------------------|------|--------------------|---------------------|

| <b>6V</b>           | -2.0 |                    |                     |

| <b>8V</b>           | -2.0 |                    |                     |

| <b>10V</b>          | -2.0 |                    |                     |

| <b>12V</b>          | -2.0 |                    |                     |

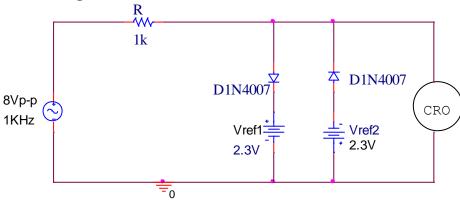

# Clipping at two independent levels

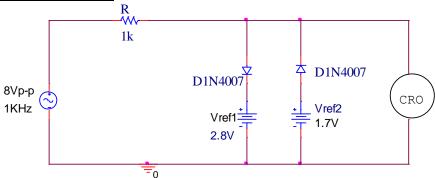

Circuit diagram:

Fig. 1.11: Two independent level clipping circuit.

# **Design:**

To obtain a slice of input voltage between 1V and 3V

Let V<sub>ref1</sub>>V<sub>ref2</sub>

$V_{o(max)}=3.5V$

And  $V_{o(max)} = V_d - V_{ref1}$

$\therefore V_{refl} = V_{o(max)} + V_{d} = 1.7V.$

$V_{o(min)}=1V$

And  $V_{o(min)} = V_d + V_{ref2}$

$\therefore V_{ref2} = V_{o(max)} - V_{d} = 2.8V.$

Choose the value of R such that the current in the circuit must lie between 1mA to 10mA.

Let current be 1mA

Then

$$R = \frac{V_{i(max)} - V_{o(max)}}{I} = \frac{4 - 3.5}{1m} = 500\Omega$$

Choose  $R=470\Omega$

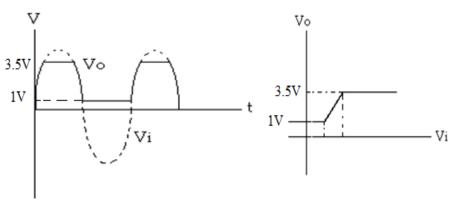

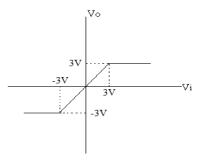

# **Expected waveform:**

Fig. 1.12: Output waveform and transfer characteristics

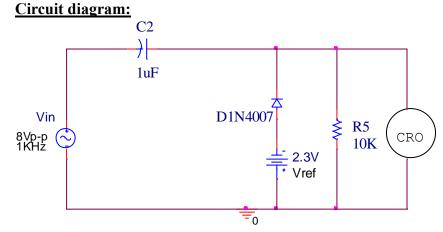

# Double ended clipping (symmetrical square wave generator)

# Circuit diagram:

Fig. 1.13: Double ended clipping circuit (symmetrical square wave generator)

# **Design:**

To generate a symmetrical square wave of  $\pm 3V$

i.e

$$V_{o(max)} = 3V \& V_{o(min)} = -3V$$

$$V_{o(max)} = V_d + V_{ref1}$$

$$V_{ref1} = V_{o(max)} - V_d = 3.0 - 0.7 = 2.3V$$

$$V_{o(min)} = V_d + V_{ref2}$$

$$V_{ref2} = V_{o(min)} - V_d = 3.0 - 0.7 = 2.3V$$

Choose the value of R such that the current in the circuit must lie between 1mA to 10mA.

### Let current be 1mA

Then

$$R = \frac{V_{i(max)} - V_{o(max)}}{I} = \frac{4-3}{1m} = 1000\Omega$$

Choose  $R=1K\Omega$

# **Expected waveform:**

Fig. 1.14: Output waveform and transfer characteristics

### **Procedure:**

- Make the Connections as per the circuit diagram

- $\triangleright$  Apply sinusoidal input  $V_i$  of 1 KHz frequency and of amplitude  $8V_{p-p}$  and set the reference voltage as per the design.

- ➤ Observe the output signal in the CRO and verify it with given waveforms.

- ➤ Apply Vi and Vo to the X and Y channel of CRO and observe the transfer characteristic waveform and verify it.

- Trace the input, output waveforms and the transfer characteristics on a trace sheet.

AY 2023-24

**Result:** The clipping circuits are design and output waveforms are verified.

**Outcome:** at the end of the experiment, Student learns the technique removing any unwanted portion in a given wave form. He/she understands the concept of wave shaping in general

# **CLAMPER CIRCUITS**

**Objective:** Design and test positive and negative clamping circuit for a given reference voltage

### **Apparatus Required:**

| SL. No | Particular         | Range    | Quantity    |

|--------|--------------------|----------|-------------|

| 1      | Bread board        |          |             |

| 2      | CRO                |          |             |

| 3      | Power supply       | DC 0-20V |             |

| 5      | Resistors          | 10ΚΩ     |             |

| 6      | Capacitor          | 1μF      |             |

| 7      | Diodes             | 1N4007   |             |

| 8      | Function generator |          | As required |

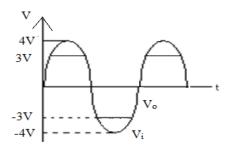

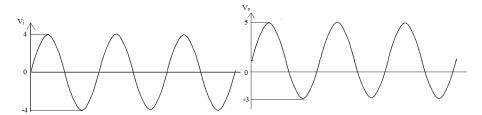

# **Negative clamper**

# **Circuit diagram:**

Fig. 1.15: Negative clamper circuit

# **Design:**

To design a clamping circuit to clamp negative peak of output voltage at 3V

$$V_{o(max)} = V_{ref} + V_d = 3V$$

$$V_{ref} = V_{o(max)} - V_d = 2.3V$$

Given frequency =1KHz.

$$\therefore T = \frac{1}{f} = 1 \text{msec}$$

The value of R and C must be selected such that  $RC \gg T$ Let RC=10T=10\*1msec=10msec.

Let C=1 $\mu$ F then R=10K $\Omega$

## **Expected waveforms:**

Fig. 1.16: Input & output Waveforms of negative clamping circuit

# **Procedure:**

- Make the connection as per the circuit diagram.

- > Apply sinusoidal input signal of 8V P-P from signal

- generator and set the reference voltage to the designed value.

- ➤ Observe the output waveform in the CRO and trace the input and output waveforms on trace sheet.

- ➤ Note down the readings from the CRO and compare it with the expected values.

# **Positive clamper**

Fig. 1.17: Positive clamper circuit

## **Design:**

To design a clamping circuit to clamp negative peak of output voltage at 3V

$$V_{o(max)} = V_{ref} + V_d = 5V$$

$$V_{ref} = V_{o(max)} - V_d = 2.3V$$

Given frequency =1 KHz.

$$T = \frac{1}{f} = 1 \text{msec}$$

The value of R and C must be selected such that RC >> T Let RC=10T=10\*1msec=10msec.

Let C=1 $\mu$ F then R=10K $\Omega$

# **Waveforms:**

Fig. 1.18: Input & output Waveforms of positive clamping circuit

### **Procedure:**

- Make the connection as per the circuit diagram.

- ➤ Apply sinusoidal input signal of 8V P-P from signal generator and set the reference voltage to the designed value.

- ➤ Observe the output waveform in the CRO and trace the input and output waveforms on trace sheet.

- ➤ Note down the readings from the CRO and compare it with the expected values.

**Result:** The clipping circuits are design and output waveforms are verified.

**Outcome:** at the end of the experiment, Student learns how to shift a given waveform to the specific dc level by manipulation of the active devices.

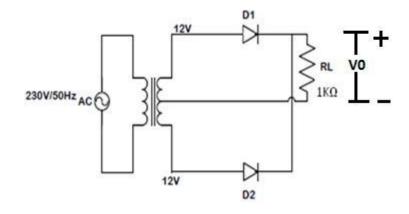

**Experiment No: 02** Date:

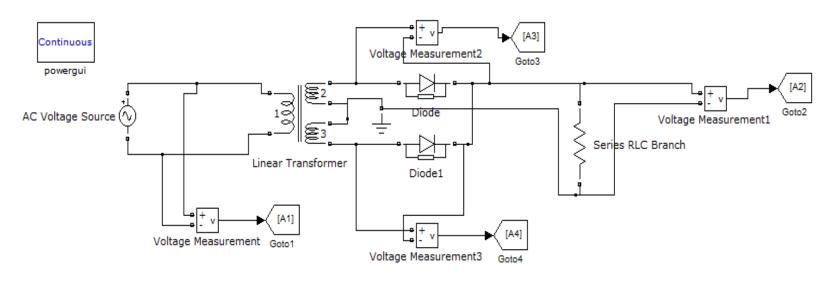

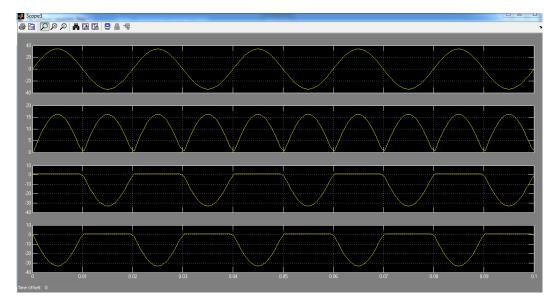

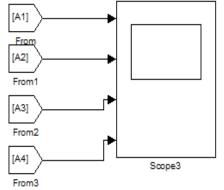

Design and Testing of Full wave -centre tapped transformer type and Bridge type rectifier circuits with and without Capacitor filter. Determination of ripple factor, regulation and efficiency

**objective:** -To design and testing of Full wave –centre tapped transformer type and Bridge type rectifier circuits with and without Capacitor filter. Determination of ripple factor, regulation and efficiency

# **Apparatus Required:**

| SL.No | Particular Particular            | Range      | Quantity |

|-------|----------------------------------|------------|----------|

| 1     | Transformer                      | 12V/19V    | 01       |

| 2     | Diode(IN4001)                    | -          | 4        |

| 3     | Resistor and capacitors          | 1KΩ, 100μF | 2        |

| 4     | Multimeter                       | -          | 1        |

| 5     | CRO Probes                       | -          | 2 set    |

| 6     | Bread Board and connecting wires | -          | 1        |

### Theory

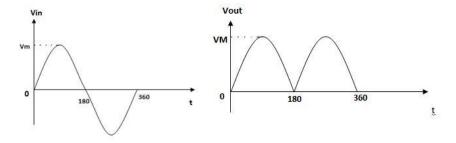

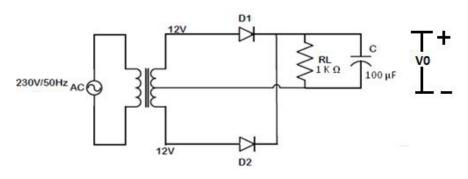

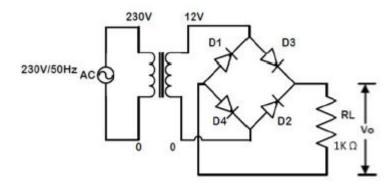

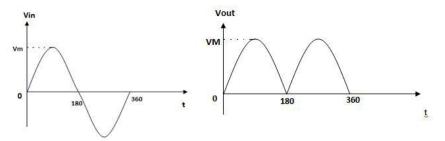

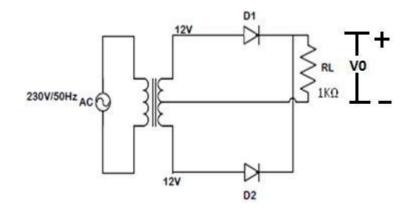

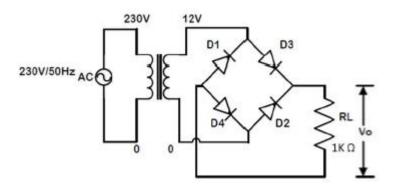

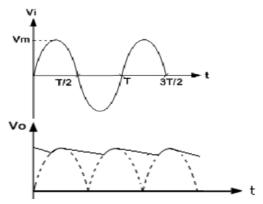

Rectifier is a circuit which converts AC to pulsating DC. Rectifiers are used in construction of DC power supplies. There are three types of rectifiers namely Half wave rectifier, Centre tap full wave rectifier and bridge rectifier.

In half wave rectification, either the positive or negative half of the AC wave is passed, while the other half is blocked. Because only one half of the input waveform reaches the output, it is very inefficient if used for power transfer.

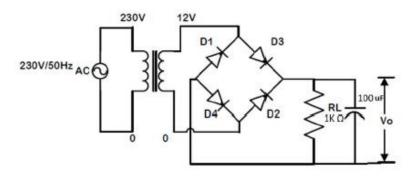

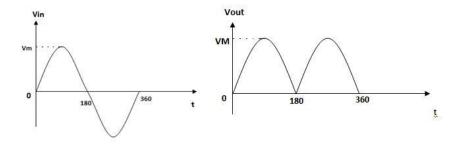

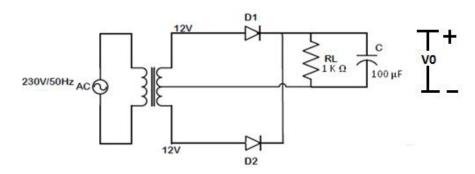

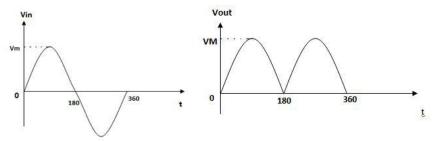

A full-wave rectifier converts the whole of the input waveform to one of constant polarity (positive or negative) at its output. Full-wave rectification converts both polarities of the input waveform to DC (direct current), and is more efficient. Fullwave rectification can be obtained either by using center tap transformer or by using bridge rectifier.

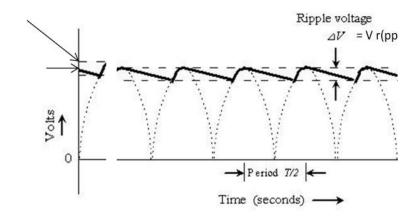

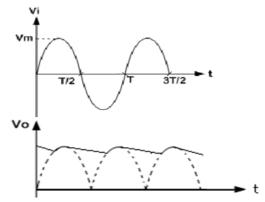

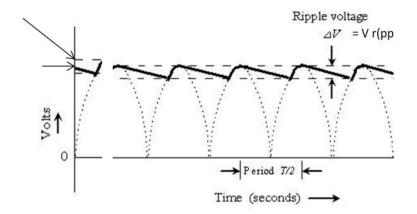

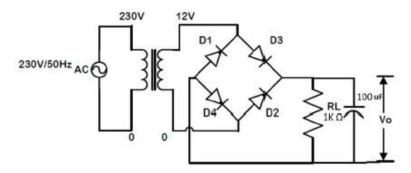

The output of a rectifier is not a smooth DC it consists of ac ripples therefore to convert this pulsating DC in to smooth DC we use a circuit called filter. There are many types of filters like C filter, L filter, LC filter, multiple LC filter,  $\pi$  filter etc..of all these C filter is the most fundamental filter.

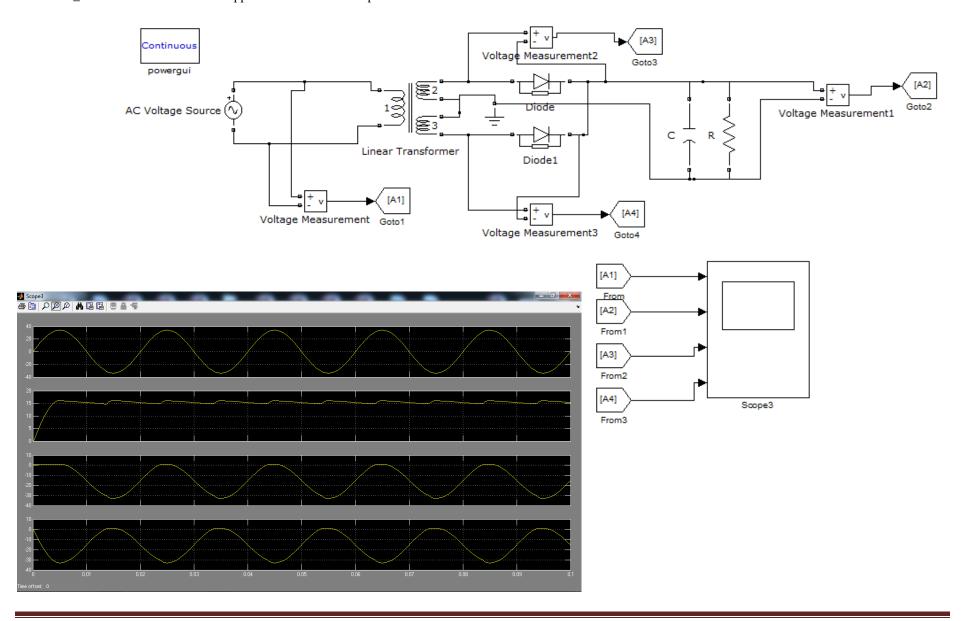

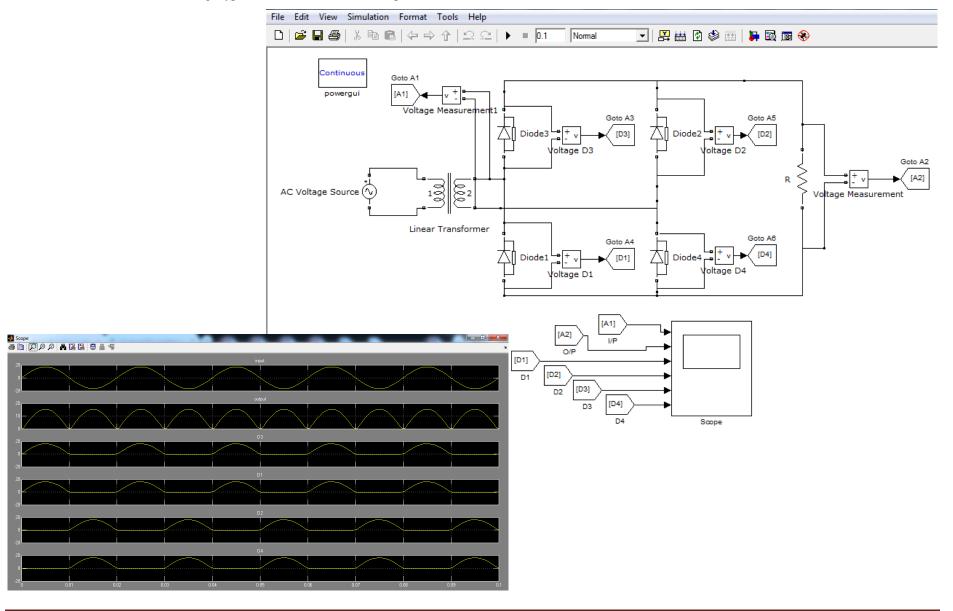

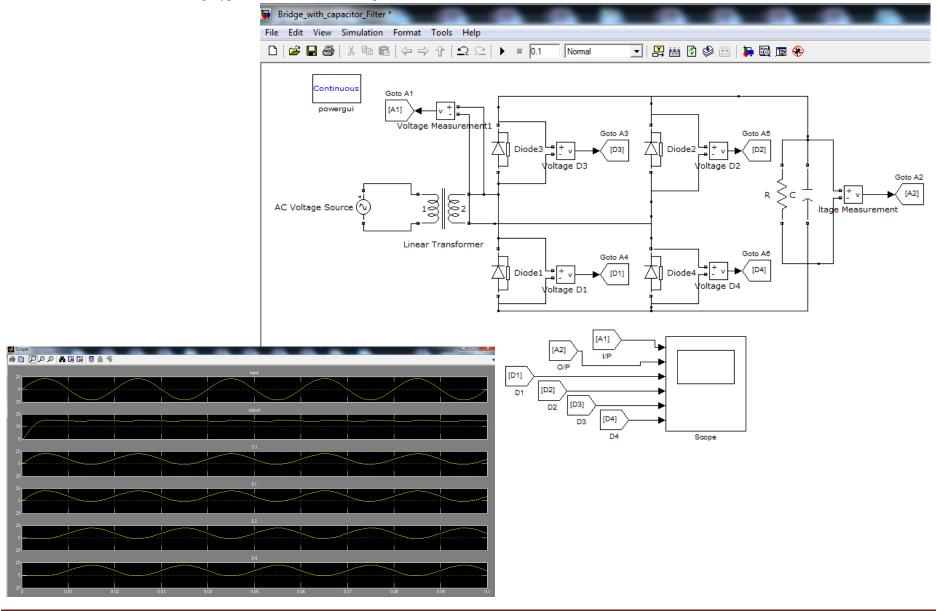

### **Circuit Diagram:**

Fig. 1.1 Circuit of full wave rectifier without filter

Fig. 1.2 Waveform for full wave rectifier without filter

# Calculations: Full wave rectifier without filter

#### **Under No Load**

$V_{M (NL)} = \underline{\hspace{1cm}} V (Peak value of voltage from CRO)$

$$V_{DC}$$

is dc (average) value,  $V_{DC}$  (NL) =  $\left(\frac{2V_{M(NL)}}{\pi}\right)$  = \_\_\_\_\_\_  $V$

AY 2023-24

Full-Load readings:

Peak Output Voltage, V<sub>M</sub> = \_\_\_\_\_V

Average value

$$V_{DC} = \frac{2V_M}{\pi} = V_{DC(FL)} = ----V$$

$$V_{RMS} = \frac{V_M}{\sqrt{2}}$$

$$V_{AC} = \sqrt{V_{RMS}^2 - V_{DC}^2}$$

Ripple Factor  $\gamma = V_{AC}/V_{DC} =$

$$P_{DC} = V_{DC}^2 / R_L =$$

$$P_{AC} = V_{RMS}^2 / R_L =$$

$$\eta = (P_{DC}/P_{AC})*100$$

% Regulation =

$$\frac{V_{DC(NL)}-VDC_{(FL)}}{V_{DC(FL)}} * 100 =$$

The peak inverse voltage for each diode is PIV =  $2V_{p(out)}$  + 0.7 V =

Fig. 1.3 Circuit of full wave rectifier with capacitor filter

Fig. 1.4 Waveform for full wave rectifier with filter

## Full wave rectifier with filter

$V_{(NL)} = \underline{\hspace{1cm}} V$

Full-Load readings:

Peak Output Voltage, V<sub>M</sub> = \_\_\_\_\_V

Ripple Factor  $\gamma = V_{AC}/V_{DC}$

$$V_{DC} = \frac{2V_M}{\pi} = V_{DC(FL)} =$$

$R=R_L$

$$V_{AC} = \frac{Vr(p-p)}{2\sqrt{3}}$$

$$V_{RMS=} \sqrt{V_{AC}^2 + V_{DC}^2}$$

$$P_{DC} = V_{DC}^2 / R_{L} =$$

$$Pac = V_{RMS}^2 / R_L =$$

$$\eta = (P_{DC}/P_{AC})*100$$

% Regulation =

$$\frac{V_{DC(NL)}-V_{DC(FL)}}{V_{DC(FL)}} * 100 =$$

Fig. 1.5 Circuit of bridge rectifier without capacitor filter

Fig. 1.6 Waveform for bridge rectifier with without filter

Fig. 1.7 Circuit of bridge rectifier with capacitor filter

**4** Calculation and formula are same as full wave bridge rectifier.

#### **Procedure:**

### Without Capacitor:

- 1. Connections are made as shown in the circuit diagram.

- 2. Measure the voltage across the terminals when the resistor is open circuited (No Load:-take it as  $V_{\text{NL}}$ ).

- 3. Connect the load resistor across the output terminals and note, the peak voltage from DSO (  $V_{\text{M}}$  )

- 4. Repeat the above procedure for full wave rectifier and bridge rectifier.

- 5. Switch off the supply

### With Capacitor:

- 1. Connections are made as shown in the Figure 2 for half wave rectifier circuit with Capacitor.

- 2. Using DSO measure the voltage across the terminals when the resistor is open circuited (No load: take it as VNL) but capacitor is connected.

- 3. Connect the load resistor across the output terminals and note, the peak voltage from DSO (VM)

- 4. Repeat the above procedure for full wave rectifier and bridge rectifier with Capacitor.

- 5. Switch off the supply and remove the connections

#### **Result:**

Table 1.1 Comparison of Rectifier

| Rectifier<br>Type | Without Filter |            |            | Without Filter |            |            |

|-------------------|----------------|------------|------------|----------------|------------|------------|

|                   | Ripple factor  | Efficiency | Regulation | Ripple factor  | Efficiency | Regulation |

| FWR               |                |            |            |                |            |            |

| BR                |                |            |            |                |            |            |

#### **Conclusions:**

#### Vive Voce

- 1. What is the function of a bridge rectifier?

- 2. Why do we need ripple factor?

- 3. Why capacitor is used in bridge rectifier?

| Preparation(4) | Conduction(4) | Result/Conclusion(5) | Total(13) |

|----------------|---------------|----------------------|-----------|

|                |               |                      |           |

|                |               |                      |           |

|                |               |                      |           |

Signature with date

**Experiment No: 03**

#### Date:

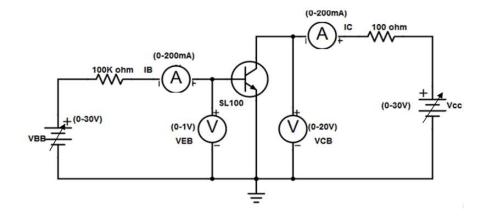

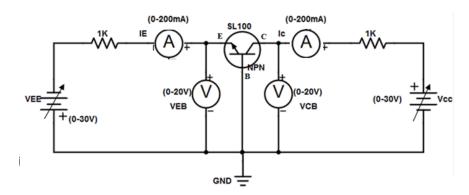

# Static Transistor characteristics for CE, CB and CC modes and determination of h parameters

**Objective:** To determine the h-parameters of CE, CB and CC modes of transistor with the help of static characteristics.

### **Common Emitter Configuration:**

### **Apparatus Required:**

| SL.No | Particular               | Range          | Quantity    |

|-------|--------------------------|----------------|-------------|

| 1     | Bread board              |                | 1           |

| 2     | CRO                      |                | 1           |

| 3     | Power supply             | DC 0-30V       | 2           |

| 5     | Transistor               | CL100/SL100    | 1           |

| 6     | Resistors                | 100kΩ, $100$ Ω | 1           |

|       | Voltmeters               | 0-20V          | 2           |

|       | Ammeters                 | 0-200mA        | 1           |

| 9     | Connecting wire and prob |                | As required |

#### Theory:

A transistor is a three terminal device. The terminals are emitter, base, collector. In common emitter configuration, input voltage is applied between base and emitter terminals and output is taken across the collector and emitter terminals. Therefore the emitter terminal is common to both input and output. The input characteristics resemble that of a forward biased diode curve. This is expected since the Base-Emitter junction of the transistor is forward biased. As compared to CB arrangement  $I_B$  increases less rapidly with  $V_{BE}$ . Therefore input resistance of CE circuit is higher than that of CB circuit. The output characteristics are drawn between Ic and  $V_{CE}$  at constant  $I_B$ , the collector current varies with  $V_{CE}$  unto few volts only. After this the collector current becomes almost constant, and independent of  $V_{CE}$ . The value of  $V_{CE}$  up to which the collector current changes with  $V_{CE}$  is known as Knee voltage. The transistor always operated in the region above Knee voltage,  $I_C$  is always constant and is approximately equal to  $I_B$ .

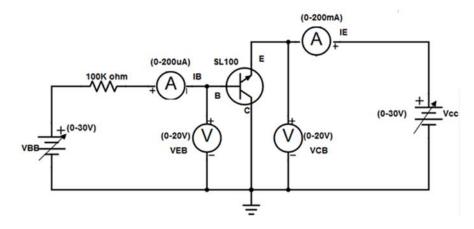

#### Circuit diagram:

Fig.2.1: Circuit diagram of Transistor Common Emitter Configuration

#### **Procedure:**

#### **Input Characteristics:**

- 1. Connect the circuit as per the circuit diagram.

- 2. For plotting the input characteristics the output voltage  $V_{\text{CE}}$  is kept constant at 1V and for different values of  $V_{\text{BE}}$ . Note down the values of  $I_{\text{C}}$

- 3. Repeat the above step by keeping  $V_{CE}$  at 2V and 4V.

- 4. Tabulate all the readings.

- 5. plot the graph between  $V_{BE}$  and  $I_{B}$  for constant  $V_{CE}$ .

### **Output Characteristics:**

- 1. Connect the circuit as per the circuit diagram

- 2. For plotting the output characteristics the input current  $I_B$  is kept constant at  $10\mu A$  and for different values of  $V_{CE}$  note down the values of  $I_C$

- 3. Repeat the above step by keeping  $I_B$  at 75  $\mu A$  100  $\mu A$

- 4. Tabulate the all the readings

- 5. Plot the graph between  $V_{\text{CE}}$  and  $I_{\text{C}}$  for constant  $I_{\text{B}}$ ,

### **Tabular Column:**

### **Input characteristics**

| input characteristics |             |                   |              |                 |              |                 |              |

|-----------------------|-------------|-------------------|--------------|-----------------|--------------|-----------------|--------------|

| Sl.                   | 17 (17)     | V <sub>CE</sub> : | =1V          | V <sub>CE</sub> | =2V          | V <sub>CE</sub> | =5V          |

| No                    | $V_{BB}(V)$ | $V_{BE}(V)$       | $I_B(\mu A)$ | $V_{BE}(V)$     | $I_B(\mu A)$ | $V_{BE}(V)$     | $I_B(\mu A)$ |

|                       | 0.1         |                   |              |                 |              |                 |              |

|                       | 0.2         |                   |              |                 |              |                 |              |

|                       | 0.3         |                   |              |                 |              |                 |              |

|                       | 0.4         |                   |              |                 |              |                 |              |

|                       | 0.5         |                   |              |                 |              |                 |              |

|                       | 0.6         |                   |              |                 |              |                 |              |

|                       | 0.7         |                   |              |                 |              |                 |              |

|                       | 0.8         |                   |              |                 |              |                 |              |

|                       | 0.9         |                   |              |                 |              |                 |              |

|                       | 1           |                   |              |                 |              |                 |              |

|                       | 2           |                   |              |                 |              |                 |              |

|                       | 3           |                   |              |                 |              |                 |              |

|                       |             |                   |              |                 |              |                 |              |

|                       | 10          |                   |              |                 |              |                 |              |

### **Output Characteristics:**

| C1        | $V_{CC}$ | $I_{B}=1$   | 0μΑ            | $I_B = 5$   | θμΑ            | $I_B = 7$   | 5μΑ            | $I_{B} = 10$ | 00μΑ           |

|-----------|----------|-------------|----------------|-------------|----------------|-------------|----------------|--------------|----------------|

| Sl.<br>No |          | $V_{B}$     | <sub>B</sub> = | $V_{B}$     | <sub>B</sub> = | $V_{\rm B}$ | <sub>B</sub> = | $V_{B1}$     | <sub>B</sub> = |

| NO        |          | $V_{CE}(V)$ | $I_{C}(\mu A)$ | $V_{CE}(V)$ | $I_{C}(\mu A)$ | $V_{CE}(V)$ | $I_{C}(\mu A)$ | $V_{CE}(V)$  | $I_C(\mu A)$   |

|           |          | 0.1         |                | 0.1         |                | 0.1         |                | 0.1          |                |

|           |          | 0.2         |                | 0.2         |                | 0.2         |                | 0.2          |                |

|           |          | 0.3         |                | 0.3         |                | 0.3         |                | 0.3          |                |

|           |          | 0.4         |                | 0.4         |                | 0.4         |                | 0.4          |                |

|           |          | 0.5         |                | 0.5         |                | 0.5         |                | 0.5          |                |

|           |          | 0.6         |                | 0.6         |                | 0.6         |                | 0.6          |                |

|           |          | 0.7         |                | 0.7         |                | 0.7         |                | 0.7          |                |

|           |          | 0.8         |                | 0.8         |                | 0.8         |                | 0.8          |                |

|           |          | 0.9         |                | 0.9         |                | 0.9         |                | 0.9          |                |

|           |          | 1           |                | 1           |                | 1           |                | 1            |                |

|           |          | 2           |                | 2           |                | 2           |                | 2            |                |

|           |          | 20          |                | 20          |                | 20          |                | 20           |                |

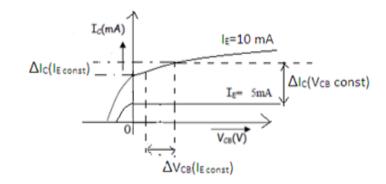

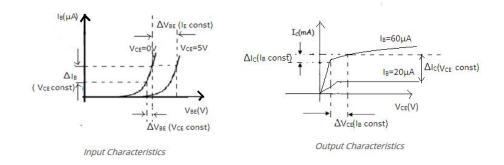

# **Typical Graph:**

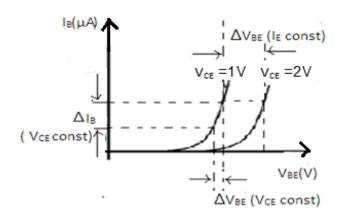

# Input Characteristics

Fig.2.2: Input Characteristics

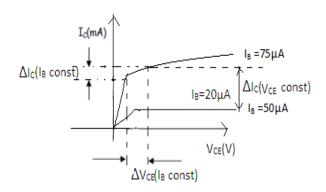

Output Characteristics

Fig.2.3: Output Characteristics

#### **Calculations:**

1. **Input Characteristics:** To obtain input resistance find  $\Delta V_{BE}$  and  $\Delta I_{B}$  for a constant  $V_{CE}$  on one of the input characteristics.

```

Input impedance = h_{ie} = R_i = \Delta V_{BE} / \Delta I_B (V_{CE} is constant)

Reverse voltage gain = h_{re} = \Delta V_{EB} / \Delta V_{CE} (I_B = constant)

```

2. Output Characteristics: To obtain output resistance find  $\Delta I_C$  and  $\Delta V_{CB}$  at a constant  $I_B$ .

```

Output admittance 1/hoe = R_o = \Delta I_C / \Delta V_{CE} (I_B is constant)

Forward current gain = hfe = \Delta I_C / \Delta I_B (V_{CE} = constant)

```

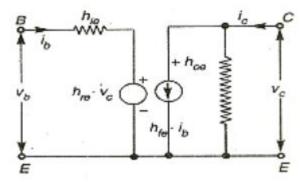

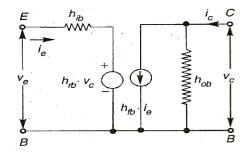

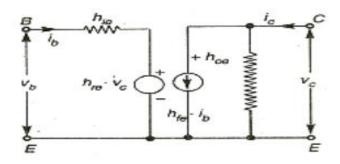

#### h - Parameter Model:

Fig.2.4: h – parameter model of common emitter configuration

### **Common Base Configuration**

### Circuit diagram:

Fig.2.5: Circuit diagram of Transistor Common Base Configuration

### **Procedure:**

### **Input Characteristics:**

- 1. Connect the circuit as shown in the circuit diagram.

- 2. Keep output voltage  $V_{CB} = 0V$  by varying  $V_{CC}$ .

- 3. Varying  $V_{EE}$  gradually, note down emitter current  $I_E$  and emitter-base voltage  $(V_{BE})$ .

- 4. Step size is not fixed because of nonlinear curve. Initially vary  $V_{EE}$  in steps of 0.1 V. Once the current starts increasing vary  $V_{EE}$  in steps of 1V up to 12V.

- 5. Repeat above procedure (step 3) for  $V_{CB} = 2V$  and 4V.

### **Output Characteristics:**

- 1. Connect the circuit as shown in the circuit diagram.

- 2. Keep emitter current  $I_E = 5 \text{mA}$  by varying  $V_{EE}$ .

- 3. Varying  $V_{CC}$  gradually in steps of 1V up to 12V and note down collector current  $I_C$  and collector-base voltage ( $V_{CB}$ ).

- 4. Repeat above procedure (step 3) for  $I_E = 10 \text{mA}$

### **Tabular Column:**

### Input characteristics

|         |                     | $V_{CB}$    | = 0         | $V_{CB} = 1V$ |             |           |

|---------|---------------------|-------------|-------------|---------------|-------------|-----------|

| SI. No. | Sl. No. $V_{EE}(V)$ | $V_{EE}(V)$ | $V_{EB}(V)$ | $I_E(mA)$     | $V_{EB}(V)$ | $I_E(mA)$ |

|         |                     |             |             |               |             |           |

|         |                     |             |             |               |             |           |

|         |                     |             |             |               |             |           |

|         |                     |             |             |               |             |           |

|         |                     |             |             |               |             |           |

|         |                     |             |             |               |             |           |

|         |                     |             |             |               |             |           |

|         |                     |             |             |               |             |           |

|         |                     |             |             |               |             |           |

# **Output Characteristics:**

| Sl. No.  | n (n)       | $I_E = 5$                | mA                                | $I_E = 10 \ mA$          |                                   |  |

|----------|-------------|--------------------------|-----------------------------------|--------------------------|-----------------------------------|--|

| 51. 110. | $V_{CC}(V)$ | V <sub>CB</sub> in Volts | <i>I<sub>c</sub></i> in m<br>Amps | V <sub>CB</sub> in Volts | <i>I<sub>C</sub></i> in m<br>Amps |  |

|          |             |                          |                                   |                          |                                   |  |

|          |             |                          |                                   |                          |                                   |  |

|          |             |                          |                                   |                          |                                   |  |

|          |             |                          |                                   |                          |                                   |  |

|          |             |                          |                                   |                          |                                   |  |

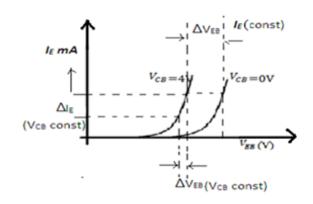

# **Typical Graph:**

Fig.2.6: Input Characteristics

Fig.2.7: Output Characteristics

#### **Calculations:**

- 1. **Input Characteristics:** To obtain input resistance, find  $\Delta V_{EE}$  and  $\Delta I_E$  for a constant  $V_{CB}$  on one of the input characteristics. Input impedance =  $h_{ib} = R_i = \Delta V_{EE} / \Delta I_E$  ( $V_{CB} = constant$ ) Reverse voltage gain =  $hrb = \Delta V_{EB} / \Delta V_{CB}$  ( $I_E = constant$ )

- 2. **Output Characteristics:** To obtain output resistance, find  $\Delta I_C$  and  $\Delta V_{CB}$  at a constant  $I_E$ .

Output admitance =  $h_{ob}$  = 1/Ro =  $\Delta I_C$  /  $\Delta V_{CB}$  ( $I_E$  = constant) Forward current gain =  $h_{fb}$  =  $\Delta I_C$  /  $\Delta I_E$  ( $V_{CB}$  = constant)

#### h - Parameter Model:

Fig.2.8: h – parameter model of common base configuration

### **Common Collector Configuration**

### Circuit diagram:

Fig.2.9: Circuit diagram of Transistor Common Collector Configuration

# **Procedure:**

# **Input Characteristics:**

- 1. Connect the circuit as shown in the circuit diagram.

- 2. Keep output voltage  $V_{CE} = 0V$  by varying  $V_{CC}$ .

- 3. Varying **V**<sub>BB</sub> gradually, note down base current **I**<sub>B</sub> and base-emitter voltage **V**<sub>BE</sub>.

- 4. Step size is not fixed because of non linear curve. Initially vary **V**<sub>BB</sub> in steps of 0.1V. Once the current starts increasing vary **V**<sub>BB</sub> in steps of 1V up to 12V.

- 5. Repeat above procedure (step 3) for  $V_{CE} = 5V$ .

# **Output Characteristics:**

- 1. Connect the circuit as shown in the circuit diagram.

- 2. Keep emitter current  $I_B = 20\mu A$  by varying  $V_{BB}$ .

- 3. Varying **V**<sub>CC</sub> gradually in steps of 1V up to 12V and note down collector current **I**<sub>C</sub> and Collector-Emitter Voltage(**V**<sub>CE</sub>).

- 4. Repeat above procedure (step 3) for  $I_B = 60\mu A$ ,  $0\mu A$ .

### **OBSERVATIONS:**

# **Input Characteristics:**

| $V_{BB}(V)$ | $V_{CE}$    | = 0          | $V_{CE} = 5V$ |              |  |

|-------------|-------------|--------------|---------------|--------------|--|

|             | $V_{BE}(V)$ | $I_B(\mu A)$ | $V_{BE}(V)$   | $I_B(\mu A)$ |  |

|             |             |              |               |              |  |

|             |             |              |               |              |  |

|             |             |              |               |              |  |

|             |             |              |               |              |  |

|             |             |              |               |              |  |

|             |             |              |               |              |  |

# **Output Characteristics:**

| $V_{cc}(V)$ | $I_B =$     | 20μΑ      | $I_B = 20 \mu AA$ |           |

|-------------|-------------|-----------|-------------------|-----------|

|             | $V_{CE}(V)$ | $I_c(mA)$ | $V_{CE}(V)$       | $I_c(mA)$ |

|             |             |           |                   |           |

|             |             |           |                   |           |

|             |             |           |                   |           |

|             |             |           |                   |           |

|             |             |           |                   |           |

|             |             |           |                   |           |

|             |             |           |                   |           |

Fig.2.10: Input Characteristics

Fig.2.11: Output Characteristics

# **Calculations from Graph:**

1. **Input Characteristics:** To obtain input resistance find  $\Delta$   $V_{BE}$  and  $\Delta I_{B}$  for a constant  $V_{CE}$  on one of the input characteristics.

Input impedance =  $h_{ie} = R_i = \Delta V_{BE} / \Delta I_B$  (Vce is constant)

Reverse voltage gain =  $h_{re} = \Delta V_{EB} / \Delta V_{CE}$  ( $I_B = constant$ )

2. **Output Characteristics:** To obtain output resistance find  $\Delta$   $\mathbf{I}_{\mathbf{C}}$  and  $\Delta \mathbf{V}_{\mathbf{C}\mathbf{B}}$  at a constant  $\mathbf{I}_{\mathbf{B}}$ .

Output admittance 1/hoe =  $R_o = \Delta I_C / \Delta V_{CE}$  (I<sub>B</sub> is constant)

Forward current gain =  $h_{fe} = \Delta I_C / \Delta I_B$  (V<sub>CE</sub> = constant)

# h – Parameter model of CE transistor:

#### **Conclusion:**

### Vive Voce

- 1. Give the comparison between CB and CC Configuration.

- 2. Mention the differences between CE and CC Configuration.

- 3. Mention the advantages of CE configuration.

| Preparation(4) | Conduction(4) | Result/Conclusion(5) | Total(13) |

|----------------|---------------|----------------------|-----------|

|                |               |                      |           |

|                |               |                      |           |

|                |               |                      |           |

**Signature with date**

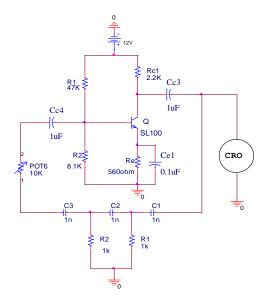

**Experiment No: 04**

Date:

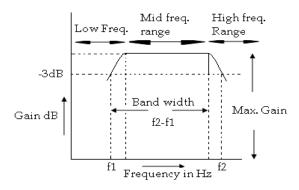

Frequency response of single stage BJT RC coupled amplifier and determination of half power points, bandwidth, input and output impedances.

**Objective:** To design RC coupled single stage amplifier using BJT and determining gain frequency response, input & output impedances.

### **Apparatus Required:**

| - Appara | tus Requireu.              |                           |             |

|----------|----------------------------|---------------------------|-------------|

| SL.No    | Particular                 | Range                     | Quantity    |

| 1        | Bread board                |                           | 1           |

| 2        | CRO                        |                           | 1           |

| 3        | Power supply               | DC 0-20V                  | 1           |

| 4        | Signal generator           | 0-2MHz                    | 1           |

| 5        | Transistor                 | CL100/SL100               | 1           |

| 6        | Resistors                  | 47KΩ, 8.1KΩ, 2.2 KΩ, 560Ω |             |

| 7        | Capacitors                 | 47uF, 0.47uF              |             |

| 8        | DRB                        | 1-100ΜΩ                   | 1           |

| 9        | Connecting wire and probes |                           | As required |

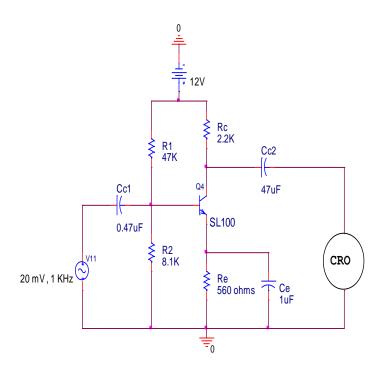

### **Design:**

Let us consider  $V_{\text{CC}}$ =12V,  $\beta$ =145,  $I_{\text{C}}$ =2mA to make transistor to work in active region.

Approximations

$$I_E \cong I_C$$

$$V_{\rm E} \cong \frac{V_{CC}}{10} = 1.2V$$

$$V_{CE} \cong \frac{V_{CC}}{2} = 6V$$

$V_B = V_{BE} + V_E = 1.2 + 0.7 = 1.9V$

To find R<sub>E</sub>:

$W.K.T V_E = I_E R_E$

$$R_E = \frac{V_E}{I_C} = 600$$

Choosing  $R_E$ =560 $\Omega$

To find Rc:

Applying KVL to output circuit

$V_{CC}\!\!=\!\!I_CR_C\!\!+\!V_{CE}\!\!+\!\!I_ER_E$

$$R_{C} = \frac{V_{CC} - V_{CE} - I_{C}R_{E}}{I_{C}} = 2400\Omega$$

Choosing R<sub>C</sub>=2.2K $\Omega$

To find  $R_1 \& R_2$ :

$$R_2 \le \frac{\beta R_E}{10}$$

$$R_2 \le \frac{560 \times 145}{10} = 8120\Omega$$

Choosing  $R_2=8.1K\Omega$

From the circuit

$$V_B = \frac{V_{CC} \times R_2}{R_1 + R_2}$$

$R_2 = 43058\Omega$

Choosing  $R_2=47K\Omega$

### To find coupling capacitors Cc:

$$f_{L} = \frac{1}{2\pi (R_{i} + R_{s})C_{C}}$$

usually  $R_{s} << R_{i}$

$$R_{i} = R_{1}ll R_{2}ll \beta r_{e}$$

$$r_{\rm e} = \frac{26\text{mV}}{I_{\rm E}} = 13$$

$$R_i = 47Kll 8.1Kll (145*13)$$

$$R_i = 1.5K$$

Let  $f_L=100Hz$

$$\therefore C_{in} = \frac{1}{2\pi \times R_i \times f_L} = 1.06 \mu F$$

Choosing  $C_C=1\mu F$

# To find Bypass capacitor C<sub>E</sub>:

$$X_{CE} \le 0.1R_{E}$$

$$i.e \frac{1}{2\pi C_{E}f} \le 0.1R_{E}$$

$$\therefore C_{E} \ge \frac{1}{0.2 \pi f R_{E}} = 28.4 \mu 8$$

Choosing C<sub>E</sub>=47µF

#### Voltage gain:

$$A_{V} = -\frac{R_{C}}{r_{e}} = -\frac{2.2K}{13} = -169$$

Negative sign indicates the phase shift of 180° between input & output

$$V_o\!\!=\!\!A_V\!\!*\!V_{in}$$

For

$$V_{in(p-p)}=20mV$$

$V_{o(p-p)}=-3.38 V$

# Circuit diagram:

Fig. 3.1: Circuit diagram for RC Coupled amplifier.

# Table 3.1: Table for RC Coupled amplifer

$V_i = 20mV$

| Frequency in Hz | $V_{o(p\text{-}p)}$ | $A_{V} = \frac{V_{o}}{V_{i}}$ | Gain in dB=20log <sub>10</sub> (V <sub>o</sub> /V <sub>i</sub> ) |

|-----------------|---------------------|-------------------------------|------------------------------------------------------------------|

| 500Hz           |                     |                               |                                                                  |

|                 |                     |                               |                                                                  |

|                 |                     |                               |                                                                  |

|                 |                     |                               |                                                                  |

|                 |                     |                               |                                                                  |

|                 |                     |                               |                                                                  |

|                 |                     |                               |                                                                  |

|                 |                     |                               |                                                                  |

|                 |                     |                               |                                                                  |

|                 |                     |                               |                                                                  |

|                 |                     |                               |                                                                  |

|                 |                     |                               |                                                                  |

| 1MHz            |                     |                               |                                                                  |

#### **Expected Waveform:**

Fig. 3.2: Frequency response graph for RC Coupled amplifier.

### **Calculations:**

Lower cut off frequency f<sub>L</sub>=-----Hz

Upper cut off frequency f<sub>U</sub>=-----Hz

Bandwidth BW=f<sub>U</sub>-f<sub>L</sub>

#### **Procedure:**

- 1. Connections are made as shown in circuit diagram

- 2. Set Vcc as 12V, and check the DC biasing conditions such that  $V_{CE}$  should be approximately equal to  $(V_{CC}/2)$  i,e 6V and  $V_{BE}$ =0.7V

- 3. If the DC biasing conditions satisfy then set the signal generator (input-voltage) amplitude (peak-to-peak sine wave) as 20mV

- 4. Vary the frequency of the input from lower range to higher range(i,e from 100Hz to 1MHz). Observe both input and output simultaneously on

- the CRO. Note the outputs voltage (peak to peak value) corresponding to the variation in frequencies of the input signal at different intervals. The output voltage remains constant at mid frequency range.

- 5. Calculate the gain and gain in DB corresponding to different values of frequencies

- 6. Plot the graph with frequency along X-axis and gain dB along Y-axis on semi log graph sheet

- 7. From the graph determine the bandwidth.

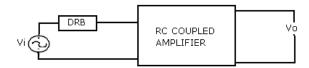

#### **Procedure to find input impedance**

Fig. 3.3: Circuit diagram for finding input impedance of a RC Coupled amplifier

- 1. Connect the circuit as shown in above figure.

- 2. Set the following

- DRB to  $0\Omega$

- Input sine wave frequency to any mid frequency.

- 3. Measure amplitude of output voltage waveform (Peak to peak Value). And denote it by  $V_{\rm a}$ .

- 4. Increase DRB from minimum value (keeping  $V_i$  constant) till  $V_o = \frac{Va}{2}$

- .The corresponding DRB reading gives the input impedance  $Z_i$  in RC coupled amplifier.

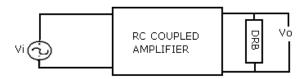

### **Procedure to find Output impedance**

Fig. 3.3: Circuit diagram for finding output impedance of a RC Coupled amplifier

- 1. Connect the circuit as shown in above figure.

- 2. Set the following

- DRB to maximum value

- Input sine wave frequency to any mid frequency.

- 3. Measure amplitude of output voltage waveform (Peak to peak Value). And denote it by  $V_{\rm b}$ .

- 4. Decrease DRB from maximum value (keeping  $V_i$  constant) till  $V_o = \frac{Vb}{2}$ . The corresponding DRB gives output impedance,  $Z_o$  of Amplifier.

#### **Conclusion:**

### **Viva Questions:**

- 1. What is Amplification?

- 2. What is transistor biasing?

- 3. What are different types of transistor biasing?

- 4. What are the Different types of Amplifiers?

- 5. State the Differences between BJT and FET?

- 6. Define operating point?

- 7. What are the different regions of operations of Transistor?

- 8. What is Stability Factor?

- 9. What are the different types of stability factors?

| Preparation(4) | Conduction(4) | Result/Conclusion(5) | Total(13) |

|----------------|---------------|----------------------|-----------|

|                |               |                      |           |

|                |               |                      |           |

|                |               |                      |           |

Signature with date

**Experiment No: 05**

Date:

Design and testing of BJT-RC phase shift oscillator for given frequency of oscillation

**objective:** To design and test the performance of BJT RC phase shift oscillator for f<sub>0</sub>=10 KHz

### **Apparatus Required:**

| SL.No | Particular    | Range                     | Quantity |

|-------|---------------|---------------------------|----------|

| 1     | Bread board   |                           |          |

| 2     | CRO           |                           |          |

| 3     | Power supply  | DC 0-20V                  |          |

| 4     | Transistor    | SL100                     |          |

| 5     | Resistors     | 47ΚΩ, 8.1ΚΩ, 2.2 ΚΩ, 560Ω |          |

| 6     | Potentiometer | 10K                       |          |

| 7     | Capacitors    | 47uF, 1uF,                |          |

**Theory:** The oscillators are an important class of circuits that are used in almost every electronics systems. These are used to produce sinusoidal and square wave forms. The square wave is used as clocks in computers & other digital systems. Oscillators are basically an amplifier with positive feedback. No input signal is required to start oscillator only certain conditions are required to be fulfilled for sustained oscillation, they are.

- > The loop gain of the circuit must be equal to 1

- > The phase shift around the circuit is zero

These two condition is called barkhausen criteria.

The RC phase shift oscillators are low frequency oscillators. These will generate oscillations in audio frequency range. The feedback network consist of three identical RC sections. The R &C values must be selected such that each RC section should provide a phase shift of  $60^{\circ}$  at desired frequency of oscillation. Hence  $180^{\circ}$  phase shift will be introduced from 3 RC sections.

The frequency of oscillation is given by,

$$f = \frac{1}{2\pi RC\sqrt{6 + 4\frac{R_C}{R}}}$$

For closed loop gain to be equal to one, the current gain of the transistor ( $h_{fe}$ ) must satisfy the condition

$$h_{fe} \ge 23 + 29 \frac{R}{R_C} + 4 \frac{R_C}{R}$$

#### Circuit diagram:

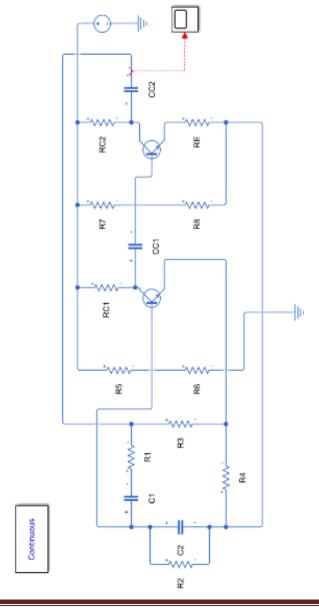

Fig4.1: RC phase shift oscillator

### Design:

Let us consider  $V_{CC}$ =12V,  $\beta$ =145,  $I_{C}$ =2mA to make transistor to work in active region.

Approximations

$$I_E \cong I_C$$

$$V_{\rm E} \cong \frac{V_{CC}}{10} = 1.2V$$

$$V_{CE} \cong \frac{V_{CC}}{2} = 6V$$

$V_B = V_{BE} + V_E = 1.2 + 0.7 = 1.9V$

### To find R<sub>E</sub>:

$W.K.T V_E = I_E R_E$

$$R_E = \frac{V_E}{I_C} = 600$$

Choosing  $R_E=560\Omega$

#### To find Rc:

Applying KVL to output circuit

$V_{CC}=I_CR_C+V_{CE}+I_ER_E$

$$R_{C} = \frac{V_{CC} - V_{CE} - I_{C}R_{E}}{I_{C}} = 2400\Omega$$

Choosing  $R_C=2.2K\Omega$

To find  $R_1 \& R_2$ :

$$R_2 \le \frac{\beta R_E}{10}$$

$$R_2 \le \frac{560 \times 145}{10} = 8120\Omega$$

Choosing  $R_2=8.1K\Omega$

From the circuit

$$V_B = \frac{V_{CC} \times R_2}{R_1 + R_2}$$

$R_2 = 43058\Omega$

Choosing  $R_2=47K\Omega$

To find coupling capacitors C<sub>C</sub>:

$$f_{L} = \frac{1}{2\pi(R_{i} + R_{s})C_{C}}$$

usually R<sub>s</sub> << R<sub>i</sub>

$$R_i = R_1 ll R_2 ll \beta r_e$$

$$r_{\rm e} = \frac{26 \text{mV}}{I_{\rm E}} = 13$$

$R_i = 47Kll \, 8.1Kll \, (145*13)$

$$R_{i} = 1.5K$$

Let  $f_L=100Hz$

$$\therefore C_{in} = \frac{1}{2\pi \times R_i \times f_L} = 1.06 \mu F$$

Choosing  $C_C=1\mu F$

To find Bypass capacitor C<sub>E</sub>:

$$X_{CE} \le 0.1R_{E} \text{ i.e } \frac{1}{2\pi\pi f_{E}} \le 0.1R_{E}$$

$$\therefore C_{E} \ge \frac{1}{0.2\pi.2} = 28.4 \mu F$$

Choosing  $C_E=47\mu F$

#### Feedback network:

The R &C values must be selected such that each RC section should provide a phase shift of 60° at desired frequency of oscillation. Hence 180° phase shift will be introduced from 3 RC sections.

From phasor diagram  $\phi = \tan^{-1} \left( \frac{X_C}{R} \right)$

$$\therefore \frac{X_C}{R} = \tan 60 = 1.73$$

Choose C=1nF then  $X_C$ =15915 $\Omega$

$$R = \frac{15915}{1.73} = 9188\Omega$$

Choosing R= $8.1K\Omega$

Check condition for sustained oscillation

$$h_{fe} \ge 23 + 29 \frac{R}{R_C} + 4 \frac{R_C}{R}$$

$145 \ge 131$

Hence the condition is satisfied.

#### **Procedure:**

- 1. Make the Connections as shown in circuit diagram.

- 2. Set Vcc as 12V, and check the DC biasing conditions such that  $V_{CE}$  should be approximately equal to  $(V_{CC}/2)$  i,e 6V and  $V_{BE}$ =0.7V.

- 3. Vary  $10K\Omega$  potentiometer so as to get an undistorted sine wave at the output.

- 4. Note the phase shift between 3 sections of RC network with respect to the output wave.

- 5. Sketch the output wave and waveforms at 3 sections of RC network.

Result

| F <sub>o</sub> in KHz | $\theta_1$ | $\theta_2$ | $\theta_3$ |

|-----------------------|------------|------------|------------|

| Theoretical           | 60         | 120        | 180        |

| Practical             |            |            |            |

**Observation:** The RC phase shift oscillator circuit is designed and studied. The crystal frequency and practical frequency of oscillations was found to be almost matching

## Vive Voce

- 1. Define Oscillator.

- 2. Give the difference between positive feedback and negative feedback.

- 3. Mention the types of oscillator circuits.

| Preparation(4) | Conduction(4) | <b>Result/Conclusion(5)</b> | Total(13) |

|----------------|---------------|-----------------------------|-----------|

|                |               |                             |           |

|                |               |                             |           |

|                |               |                             |           |

Signature with date

#### **EXPERIMENT NO. 6:**

## <u>Design and testing of Hartley and Colpitt's oscillator for given</u> <u>frequency of oscillation</u>

**Objective:** To design and test the performance of BJT colpitts and Hartley oscillator for radio frequency range of  $f_0$ =100 Khz.

## **Components required:**

| Component        | Specification                     |

|------------------|-----------------------------------|

| Bread board      |                                   |

| CRO              |                                   |

| Power supply     | DC 0-20V                          |

| Signal generator | 0-2Mhz                            |

| Transistor       | SL100                             |

| Resistors        | 47KΩ, $8.1$ KΩ, $2.2$ KΩ, $560$ Ω |

| Capacitors       | 47uF, 1uF,                        |

| DIB              |                                   |

| DCB              |                                   |

**Theory:** These are basically tuned oscillators. These oscillators are used to generate oscillations in frequency ranging from 100KHz to hundred of MHz. The split capacitor or inductor arrangement is called the tank circuit and this introduces the required 180° phase shift for output voltage.

## **Hartley oscillator:**

## Circuit diagram:

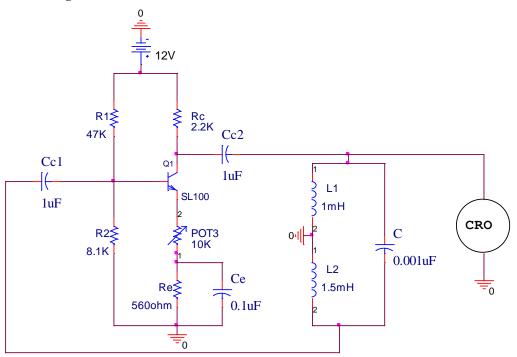

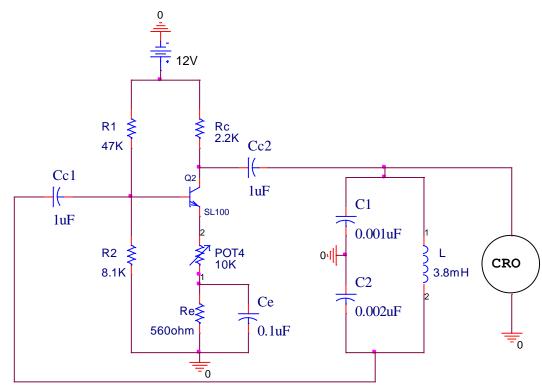

Fig. 9.1: Hartley oscillator circuit

## **Design:**

Let us consider  $V_{CC}$ =12V,  $\beta$ =145,  $I_{C}$ =2mA to make transistor to work in active region.

Approximations

$$I_E \cong I_C$$

$$V_{\rm E} \cong \frac{V_{CC}}{10} = 1.2V$$

$$V_{CE} \cong \frac{V_{CC}}{2} = 6V$$

$V_{B} = V_{BE} + V_{E} = 1.2 + 0.7 = 1.9V$

## To find R<sub>E</sub>:

$$W.K.T V_E = I_E R_E$$

$$R_E = \frac{V_E}{I_C} = 600$$

Choosing  $R_E=560\Omega$

#### To find R<sub>C</sub>:

Applying KVL to output circuit

$$V_{CC}=I_{C}R_{C}+V_{CE}+I_{E}R_{E}$$

$$R_{C} = \frac{V_{CC} - V_{CE} - I_{C}R_{E}}{I_{C}} = 2400\Omega$$

Choosing  $R_C=2.2K\Omega$

## To find $R_1 \& R_2$ :

$$R_2 \le \frac{\beta R_E}{10}$$

$$R_2 \le \frac{560 \times 145}{10} = 8120\Omega$$

Choosing  $R_2=8.1K\Omega$

From the circuit

$$V_B = \frac{V_{CC} \times R_2}{R_1 + R_2}$$

$R_2 = 43058\Omega$

Choosing  $R_2=47K\Omega$

## To find coupling capacitors C<sub>C</sub>:

$$f_L = \frac{1}{2\pi\pi(_i + R_S)C_C}$$

usually  $R_s \ll R_i$

$$R_{i} = R_{1} ll R_{2} ll \beta r_{e}$$

$$r_{\rm e} = \frac{26\text{mV}}{I_{\rm E}} = 13$$

$$R_i = 47Kll 8.1Kll (145*13)$$

$$R_{i} = 1.5K$$

Let  $f_L=100Hz$

$$\therefore C_{in} = \frac{1}{2\pi \times R_i \times f_I} = 1.06 \mu F$$

Choosing  $C_C=1\mu F$

## To find Bypass capacitor C<sub>E</sub>:

$$X_{CE} \le 0.1R_E$$

i.e

$$\frac{1}{2\pi\pi f_E} \le 0.1R_E$$

$$C_{\rm E} \ge \frac{1}{0.2\pi.2} = 28.4 \mu 8$$

Choosing  $C_E=47\mu F$

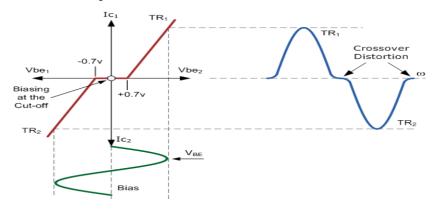

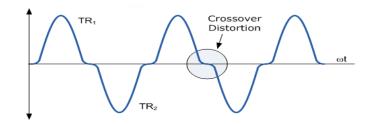

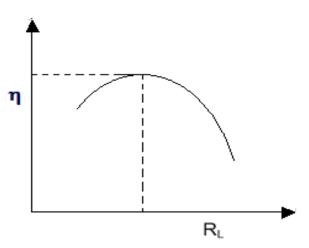

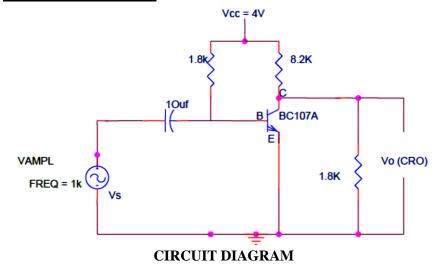

## Tank circuit: